https://eventos.utfpr.edu.br//sicite/sicite2017/index

# Implementação de algoritmos de processamento em FPGA para reconstrução de imagens biomédicas por ultrassom

#### **RESUMO**

Samuel Leme de Almeida Leite Samuel.lemeleite@gmail.com Universidade Tecnológica Federal do Paraná, Curitiba, Paraná, Brasil

Amauri Amorin Assef amauriassef@utfpr.edu.br Universidade Tecnológica Federal do Paraná, Curitiba, Paraná, BRASIL **OBJETIVO**: Este artigo apresenta uma nova metodologia para o projeto de filtros digitais baseados em dispositivos FPGA para sinais brutos de ultrassom por meio da ferramenta DSP Builder. **MÉTODOS**: Foram utilizados o Simulink, como ambiente de projeto, e a ferramenta Signal Tap II, juntamente com o *software* Nios II, para a simulação e a obtenção dos resultados em um *kit* de FPGA DE2-150. **RESULTADOS**: Como principal resultado deste trabalho, foi projetado um filtro de 8 coeficientes com estrutura simétrica utilizando apenas quatro multiplicadores e com capacidade de atualização de coeficientes via *software* em tempo real. **CONCLUSÃO**: Pode-se concluir que o objetivo deste trabalho foi concluído com sucesso. Os resultados apresentados corroboram a eficiência da utilização de dispositivos FPGA para aplicações que exigem flexibilidade e elevada velocidade de processamento.

PALAVRAS-CHAVE: DSP Builder. Filtragem digital. FPGA.

## **INTRODUÇÃO**

Os filtros digitais são sistemas utilizados em dispositivos DSP (*Digital Signal Processor*) para modificar ou retirar alguma característica do sinal podendo mudar a amplitude relativa dos componentes em frequência de um sinal ou eliminar alguns componentes em frequência (OPPENHEIM, WILLSKY, & NAWAB, 1997). Eles são divididos em duas categorias de acordo com as características da resposta ao impulso no domínio do tempo de sua função de transferência: *Infinite Impulse Response* (IIR) e o *Finite Impulse Response* (FIR). Em comparação com o filtro IIR, o filtro FIR possui as vantagens de uma fase linear exata, facilmente implementada em hardware e estabilidade do sistema (JI-FENG, SHUANG, JUN-XING, & YANING, 2015).

A equação diferencial que define este filtro é dada por:

$$y(n) = \sum_{k=0}^{N-1} h(k)x(n-k)$$

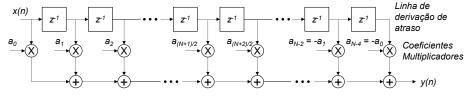

onde, N é a ordem do filtro, a resposta ao impulso h(n) são os coeficientes, x(n) é o sinal de entrada e y(n) o sinal após a filtragem. A representação da estrutura de um filtro FIR, apresentada na Figura 1, é implementada a partir da interpretação da Equação 1 do filtro discreto, onde x(n) representa o sinal de entrada a ser filtrado,  $z^{-1}$  o fator de atraso e y(n) o sinal de saída processado (JI-FENG, SHUANG, JUN-XING, & YANING, 2015; ASSEF et al., 2017).

Figura 1: Estrutura convencional generalizada de um Filtro FIR.

Fonte: Assef et al. (2017).

### **MÉTODOS**

Para o projeto do filtro digital com 8 coeficientes foi utilizado a biblioteca DSP Builder, integrada ao *software* Matlab/Simulink. Esta ferramenta foi desenvolvida pela Altera® e tem como objetivo simplificar o desenvolvimento de projetos baseados em FPGA, uma vez que não é necessário que o projetista saiba programar em VHDL, pois utiliza diagramas de blocos no Simulink e, ao final, os converte em linguagem de *hardware*, simplificando o processo.

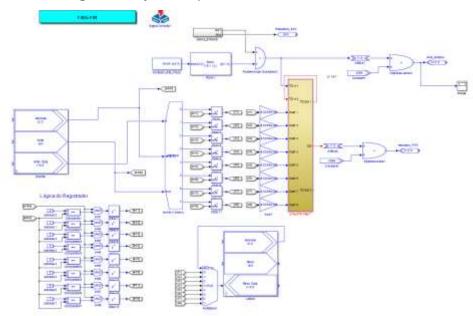

O projeto é formado basicamente por cinco grupos de blocos. O primeiro grupo é composto pelo bloco *Avalon MM Slave* que basicamente é um barramento que permite a passagem das informações paralelamente, tornando o processo mais ágil. O segundo grupo denominado lógica do registrador é composto por blocos de comparação que fazem a seleção de qual entrada será registrada no filtro. Já o terceiro grupo é composto pelos blocos de ganho e um subsistema denominado

8-TapFIR Filter, onde o filtro está projetado. Os ganhos são necessários devido a uma normalização dos coeficientes do filtro em  $[2^{16}-1]$ , pois a função em C utilizada para a atualização dos coeficientes do filtro não aceitava números pontos flutuantes. Dessa forma, os valores dos blocos de ganho estão definidos como  $[1/(2^{16})-1]$ . O quarto grupo é composto com um barramento  $Avalon\ MM\ Slave$ , configurado como leitura. O quinto e último conjunto é composto basicamente por um subsistema denominado  $Dados\_Entrada$  ao qual fica armazenado em uma ROM os sinais de ultrassom obtidas pelo professor Dr. Amauri Amorin Assef em sua tese de Doutorado (ASSEF, 2013), e por uma ROM onde é armazenado o ruído que será somado ao sinal de ultrassom, para testes de validação. Ao final do projeto, é necessário gerar o código em VHDL através do bloco  $Signal\ Compiler$ . A Figura 2 mostra o projeto completo do hardware.

Figura 2: Projeto completo do Filtro FIR com 8 coeficientes.

Fonte: Autoria própria.

### **RESULTADOS**

Os coeficientes do filtro foram gerados a partir da ferramenta FDATool do Matlab® com frequência de amostragem em 40 MHz, frequência de banda de passagem em 3,2 MHz e frequência de corte em 8 MHz, conforme Assef et al. (2017).

Como os coeficientes foram atualizados via *software*, foi necessária a utilização de uma função presente na biblioteca *system.h* no Nios II, denominada *IOWR\_16DIRECT()*, que permite a passagem de parâmetros pelo barramento paralelamente. Após a validação por simulações no Simulink e na ferramenta ModelSim, o *hardware* gerado em código VHDL e o *software* gerado em linguagem C foram gravados na FPGA Cyclone IV do *kit* DE2-115 para avaliação.

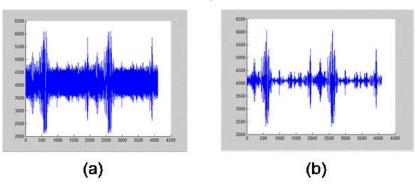

As Figuras 3(a) e 3(b) mostram a comparação entra o sinal de entrada antes da filtragem, isto é, o sinal original de ultrassom adicionado ao ruído, e o sinal de

saída depois da filtragem, processado pela FPGA. Aqui foram utilizadas 4096 amostras de entrada. O tempo total de atraso de processamento são quatro ciclos de 40 MHz, isto é, 100 ns.

Figura 3: (a) Sinal de entrada antes da filtragem; (b) Sinal de entrada após a filtragem.

Fonte: Autoria própria.

## **CONCLUSÃO**

Pode-se concluir que o objetivo deste trabalho, projeto e implementação de algoritmo filtro digital FIR passa-baixa para filtragem de sinais brutos de radiofrequência de ultrassom para aplicações biomédica, foi atingido com sucesso. Os resultados apresentados, com o projeto de um filtro com 8 coeficientes e apenas quatro circuitos de multiplicação, corroboram a eficiência da utilização de dispositivos FPGA para aplicações que exigem flexibilidade e elevada velocidade de processamento.

# Implementation of FPGA processing algorithms for reconstruction of biomedical ultrasound images

#### **ABSTRACT**

**OBJECTIVE:** This paper presents a new methodology for of digital filters design based on FPGA devices for raw ultrasonic signals using the DSP Builder tool. **METHODS:** The Simulink was used as the design environment, and the Signal Tap II tool, along with Nios II software, were used to simulate and obtain the results in a DE2-150 FPGA kit. **RESULTS:** As the main result of this work, a filter with 8 coefficients with symmetric structure was designed using only four multipliers and with the capacity to update coefficients via software in real time. **CONCLUSION:** It can be concluded that the objective of this work was successfully concluded. The results presented corroborate the efficiency of the use of FPGA devices for applications that require flexibility and high processing speed.

KEYWORDS: DSP Builder. Digital filtering. FPGA.

#### **AGRADECIMENTOS**

O presente trabalho foi realizado com o apoio da Universidade Tecnológica Federal do Paraná/Brasil. Os autores também agradecem à empresa Altera, atual Intel, pela disponibilização do *kit* FPGA utilizado e também das licenças concedidas para a utilização dos *softwares*, pois sem as mesmas nada disso seria possível.

#### **REFERÊNCIAS**

ASSEF, A. A. Arquitetura de hardware multicanal reconfigurável com excitação multinível para desenvolvimento e testes de novos métodos de geração de imagens por ultrassom [tese]. Curitiba: Universidade Tecnológica Federal do Paraná; 2013.

ASSEF, A. A.; MAIA, J. M.; FERREIRA, B. M.; SERAFIN, H. S.; BASSAN, G. M.; DE MORAES FILHO, A. F.; COSTA, E. T. **Projeto de um filtro digital FIR passa-baixa em FPGA para aplicações de processamento de sinais de ultrassom**. In: XXV Congresso Brasileiro de Engenharia Biomédica, 2016, Foz do Iguaçu. CBEB 2016, 2016.

FERREIRA, B. M. Modelagem e implementação de um sistema de processamento digital de sinais baseado em FPGA para geração de imagens por ultrassom usando o simulink [tese]. Curitiba: Universidade Tecnológica Federal do Paraná; 2017.

JI-FENG, D.; SHUANG, X.; JUN-XING, Z.; YA-NING, Y. 2015. **Filter Design Based on DSP Builder**. Disponível em < <a href="https://benthamopen.com/contents/pdf/TOEEJ/TOEEJ-9-15.pdf">https://benthamopen.com/contents/pdf/TOEEJ/TOEEJ-9-15.pdf</a> Acesso em: 07 ago. 2017

OPPENHEIM, A. V.; WILLSKY, A. S.; NAWAB, S. H. **Signals and Systems**. Prentice—Hall,, v. 1, p. 997, 1997.

Recebido: 31 ago. 2017. Aprovado: 02 out. 2017.

## Como citar:

LEITE, S. L. de A. e ASSEF, A. A. Implementação de algoritmos de processamento em FPGA para reconstrução de imagens biomédicas por ultrassom. In: SEMINÁRIO DE INICIAÇÃO CIENTÍFICA E TECNOLÓGICA DA UTFPR, 22., 2017, Londrina. **Anais eletrônicos...** Londrina: UTFPR, 2017. Disponível em: <a href="https://eventos.utfpr.edu.br//sicite/sicite/sicite/2017/index">https://eventos.utfpr.edu.br//sicite/sicite/sicite/2017/index</a>. Acesso em: XXX.

#### Correspondência:

Samuel Leme de Almeida Leite

Travessa Frei Caneca, número 39, Bairro Centro, Curitiba, Paraná, Brasil.

#### Direito autoral:

Este resumo expandido está licenciado sob os termos da Licença Creative Commons-Atribuição-NãoComercial 4.0 Internacional.