## X Seminário de Extensão e Inovação XXV Seminário de Iniciação Científica e Tecnológica

https://eventos.utfpr.edu.br//sicite/sicite2020

## Estudo comparativo de circuitos inversores lógicos CMOS e nMOS

#### Comparative study CMOS and nMOS logic inverter circuits

#### **RESUMO**

Este trabalho apresenta um estudo comparativo de características estática e dinâmica de inversores lógicos CMOS e nMOS, através de simulações computacionais dos circuitos. Neste contexto, é avaliado a influência de dois parâmetros no desempenho dos inversores: capacitância de carga e frequência do sinal de entrada. Desta forma, constata-se que no caso do inversor lógico nMOS, sua aplicação é limitada a frequências de trabalho de até dezenas de kHz, pelo fato do circuito auxiliar para chaveamento dos MOSFETs ter tempo de atraso cerca de três ordens de magnitude maior do que os tempos de transição de estado dos nMOSFETs.

PALAVRAS-CHAVE: Circuitos Integrados. Microeletrônica. Transistores.

#### **ABSTRACT**

This work presents a comparative study of static and dynamic characteristics of CMOS and nMOS logic inverters from circuit computer simulations. In this context, it is evaluated the influence of two parameters on the inverter performances: output capacitance, which is considered as a load, and the input signal frequency. Thus, it suggests that in the case of the nMOS logic inverter, its application is limited to input frequencies up to dozens of kHz, due to the fact that the used driver for switching the MOSFETs has a time delay switch around three order of magnitude higher compared to the rise and fall times of the nMOSFETs.

**KEYWORDS:** Integrated Circuits. Microelectronics. Transistors.

Thiago Roberto Machado thiagomachado376@gmail.com Universidade Tecnológica Federal do Paraná, Toledo, Paraná, Brasil

Alberto Vinícius de Oliveira avdo@utfpr.edu.br Universidade Tecnológica Federal do Paraná, Toledo, Paraná, Brasil

**Recebido:** 19 ago. 2020. **Aprovado:** 01 out. 2020.

**Direito autoral:** Este trabalho está licenciado sob os termos da Licença Creative Commons-Atribuição 4.0

### X Seminário de Ext<mark>ensão e Inovação</mark> XXV Seminário de Iniciação Científica e Tecnológica

## 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

#### **INTRODUÇÃO**

Atualmente, a eletrônica desempenha um papel fundamental no desenvolvimento da sociedade. Com a viabilidade de miniaturização de componentes eletrônicos, tornou-se possível a fabricação de circuitos integrados em escalas nanométricas, e, em decorrência deste avanço tecnológico, houve um aumento na capacidade de processamento de informações. Com isso, todos os setores de pesquisa existentes se beneficiaram, tendo em vista que cálculos complexos e processamento de imagens se tornam mais rápidos e acessíveis. Um exemplo pode ser observado em Akiyama (2019), no qual aproximadamente oito petabytes de dados foram necessários para estudo, e assim gerar a primeira imagem de um buraco negro.

Os objetos de estudo deste trabalho são os inversores CMOS e nMOS, os quais são implementados com Transistores de Efeito de Campo tipo Metal-Óxido-Semicondutor (MOSFETs). Estes circuitos possuem uma vasta gama de aplicações, desde a eletrônica digital: com aplicações em inversores lógicos, até a eletrônica de potência: com os conversores estáticos de corrente contínua para corrente alternada (CC-CA) como podem ser vistos em cite Ahmed (2004).

Neste contexto, o objetivo deste trabalho é comparar os comportamentos estático e dinâmico de circuitos inversores lógicos nMOS e CMOS, com o foco na influência das variações de capacitância de saída e de frequência de trabalho nos tempos de comutação dos circuitos.

#### REFERENCIAL TEÓRICO

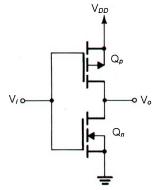

O inversor lógico complementar MOSFET (CMOS) consiste na associação de MOSFETs de canais do tipo n  $(Q_n)$  e do tipo p  $(Q_p)$ , com o terminais de porta comuns, sendo a entrada  $(V_i)$  do circuito, enquanto os terminais de drenos comuns equivalem à saída  $(V_o)$  do inversor (MARTINO, 2003), como apresentado na Figura 1.

Figura 1 - Circuito Inversor lógico CMOS

Fonte: Adaptação de Martino (2003, p. 108).

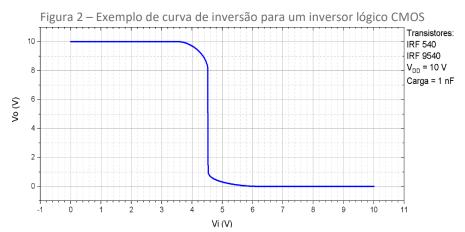

A curva característica de transferência do circuito da Figura 1, também conhecida como característica estática do inversor, demonstra o comportamento da tensão de saída do circuito em relação à variação da tensão entrada do inversor.

### X Seminário de Ext<mark>ensão e Inovação</mark> XXV Seminário de Iniciação Científica e Tecnológica

## 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

Esta curva é representada na Figura 2 e depende dos modos de operação de  $Q_n$  e de  $Q_p$ , mais detalhes são abordados em Martino (2003, p. 108).

Fonte: Adaptado de Martino (2003, p. 108).

Além do comportamento estático ilustrado na Figura 1, outro fator importante é o comportamento dinâmico do dispositivo. Nesta análise, avalia-se no domínio do tempo a resposta de tensão elétrica do inversor, ou seja,  $V_o$ , ao se aplicar um sinal em  $V_i$ . Assim, verifica-se que as transições dos estados (desligado para ligado e vice-versa) não são instantâneas. Estes intervalos nas transições são denominados como tempos de subida  $(t_r)$  e de descida  $(t_f)$ . Segundo Martino (2003, p. 114), eles podem ser determinados por:

$$t_f = \frac{4 C_l}{\beta_n V_{DD}},\tag{1}$$

$$t_r = \frac{{}^4C_l}{\beta_0 V_{DD}},\tag{2}$$

$$\beta_n = \frac{\mu_n \varepsilon_{ox}}{\chi_{ox}} \frac{W}{L},\tag{3}$$

$$\beta_p = \frac{\mu_p \varepsilon_{ox}}{t_{ox}} \frac{W}{L},\tag{4}$$

onde,  $C_l$  é capacitância de carga conectada à saída do inversor,  $\beta_n$  e  $\beta_p$  são os fatores de ganho dos MOSFETs,  $\mu_n$  é a mobilidade de elétrons,  $\mu_p$  é a mobilidade de lacunas,  $\varepsilon_{ox}$  é a permissividade do óxido de porta,  $t_{ox}$  é a espessura do óxido de porta, W é a largura do canal e L é o comprimento do canal.

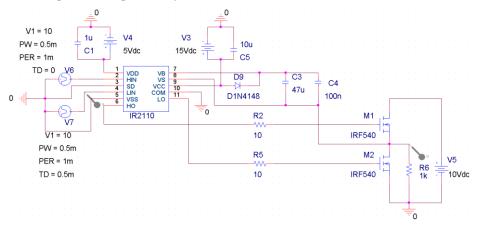

O inversor lógico nMOS consiste em utilizar somente dispositivos MOSFET de canal de tipo n. Este inversor exerce as mesmas funções que o inversor lógico CMOS. Para implementação deste circuito, é necessário utilizar um circuito auxiliar para chaveamento dos nMOSFETs, como pode ser observado em International Rectifier (2005, p. 1).

#### **MATERIAIS E MÉTODOS**

Neste trabalho a implementação do inversor CMOS é realizada com MOSFETs de enriquecimento, com os modelos comerciais IRF540 e IRF9540 (VISHAY SILICONIX, 2008a, 2008b). Por outro lado, para a implementação do circuito inversor lógico nMOS, além dos nMOSFETs IRF540, é necessário a utilização de um circuito auxiliar para acionamento dos MOSFETs, que está conectado terminal de

#### X Seminário de Ext<mark>ensão e Inovação</mark> XXV Seminário de Iniciação Científica e Tecnológica

#### 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

$V_{DD}$ . Este circuito auxiliar é denominado *driver*, e neste trabalho, utiliza-se o circuito integrado comercial IR2110 (INTERNATIONAL RECTIFIER, 2005). O circuito completo de implementação é ilustrado na Figura 3.

Figura 3 – Diagrama esquemático do inversor nMOS com driver IR2110

Fonte: Adaptado de Kovac (2019, p. 1).

O foco deste trabalho é avaliar os tempos de comutação dos circuitos inversores lógicos CMOS e nMOS. Para isso, é realizado uma análise dos tempos de subida e de descida pelo critério de 10 % e 90 % apresentado em Sedra (2013) e Martino (2003). Este método consiste em, no caso do tempo de subida, tomar como base o tempo inicial em que o valor de Vo atinge 10 % de seu valor de transição, enquanto o tempo final é tomado quando o valor de Vo atinge 90 % do valor final. No caso do tempo de descida, o procedimento é análogo.

No inversor CMOS, representado na Figura 1, os parâmetros passíveis para variação são a capacitância utilizada como carga (C<sub>i</sub>) e a frequência (f) da onda quadrada utilizada em V<sub>i</sub>. Os valores de capacitância utilizados para o capacitor de saída estão entre 1 nF e 100 nF e as frequências estão situadas dentro da faixa de 1 kHz a 1 MHz. Todos os valores são específicos na Tabela 1.

Com a variação destes parâmetros ( $C_l$  e f), verifica-se como os tempos de subida e de descida podem ser afetados.

Tabela 1 – Parâmetros de análise para estudo dos inversores lógicos

| C <sub>r</sub> (nF) | f (kHz) |

|---------------------|---------|

| 1                   | 1       |

| 10                  | 5       |

| 27                  | 10      |

| 50                  | 50      |

| 75                  | 100     |

| 100                 | 500     |

|                     | 1000    |

Fonte: Autoria Própria (2020).

Neste trabalho, adota-se a tensão lógica de 10 V como nível lógico 1, ou seja, o valor de V<sub>DD</sub>. Comumente utiliza-se 5 V, porém, devido a algumas falhas de

## X Seminário de Extensão e Inovação XXV Seminário de Iniciação Científica e Tecnológica

## 23 a 27 de Novembro | Toledo - PR

571III 66 162226

convergência no simulador, as formas de onda encontradas para as curvas de 5 V não foram satisfatórias.

#### **RESULTADOS E DISCUSSÃO**

No inversor lógico CMOS apresentado na Figura 1, estudou-se a influência da frequência do sinal de entrada (vide Tabela 1) nos tempos de subida e de descida. Uma vez que estes parâmetros não são dependentes diretos da frequência, como apresentado nas Eqs. (1) e (2), nota-se que  $t_r$  e  $t_f$ , são dependentes de características construtivas dos transistores e não do circuito inversor CMOS.

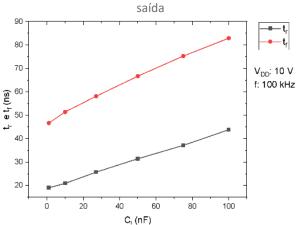

Em uma etapa seguinte, analisou-se a influência da capacitância de carga do circuito inversor CMOS nos tempos de transição de estado, como apresentado na Figura 4. Nota-se que as curvas de  $t_r$  e  $t_f$  apresentam um comportamento quase linear, este comportamento pode ser explicado pelos tempos de carga e de descarga do capacitor, ao qual sabe-se que dado um valor de resistência fixo, o valor de capacitância do capacitor é proporcional à constante de tempo  $\tau$ , característica de circuitos de primeira ordem (Resistivo-Capacitivo com fonte) os quais podem ser vistos com mais detalhes em Sadiku (2013), ou seja, o dispositivo contém mais carga acumulada, e assim tem um tempo de descarga maior.

Figura 4 – Tempos de subida e descida do inversor CMOS em função da capacitância de

Fonte: Autoria própria (2020).

Ainda na Figura 4, constata-se que o tempo de descida é aproximadamente o dobro do tempo de subida, segundo Martino (2003, p. 88), isso se deve ao fato de que a mobilidade das lacunas no pMOSFET, é de duas a três vezes menor do que a mobilidade dos elétrons no nMOSFET, ou seja, com uma mobilidade menor, levase mais tempo para transição do estado no pMOSFET.

Para utilização em componentes de circuitos integrados, a capacitância de saída (*Ci*) pode ser substituída por um MOSFET, que pode atua como carga capacitiva no lugar do capacitor. Neste cenário, avaliou-se a influência da capacitância de saída na curva de transferência do inversor CMOS, porém, o circuito presente na saída dispositivo não alterou significativamente a curva de transferência do circuito, uma vez que, essa curva depende dos modos de operação dos transistores, e estes não foram alterados pela variação de *Ci*.

## X Seminário de Extensão e Inovação XXV Seminário de Iniciação Científica e Tecnológica

## 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

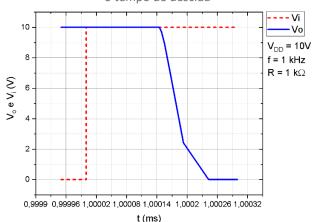

Nas Figuras Figura 5 e Figura 6 são demonstradas as formas de onda para os tempos de subida e de descida, respectivamente, para circuito inversor lógico nMOS ilustrado na Figura 3. Nota-se que  $t_r$  e  $t_f$  são diretamente afetados pelo atraso proporcionado pelo *driver*, aumentando de ns para  $\mu$ s. Neste caso, além de  $t_r$  e  $t_f$ , o intervalo de tempo que o *driver* leva para enviar o sinal de chaveamento do circuito também deve ser considerado, uma vez que há um atraso de aproximadamente 15  $\mu$ s para chaveamento dos transistores. Assim, adotando-se a soma do critério de 10 % e 90 % com os 15  $\mu$ s necessários para o chaveamento, obtém-se que os tempos de subida e de descida com o *driver* são de aproximadamente 20  $\mu$ s.

Figura 5 – Níveis de tensão de entrada e saída do inversor lógico nMOS com o *driver* para

Fonte: Autoria própria (2020).

Figura 6 – Níveis de tensão de entrada e saída do inversor lógico nMOS com o *driver* para o tempo de descida

Fonte: Autoria própria (2020).

O fato dos tempos de subida e de descida possuírem aproximadamente o mesmo valor era um fato esperado, pois de acordo com Vishay Siliconix (2008a), o tempo de subida e descida é na ordem de 50 ns. Logo, o atraso observado nas Figura 5 e Figura 6 é proporcionado predominantemente pelo *driver*. Apesar do tempo de atraso ter aumentado drasticamente, o circuito ainda apresenta um tempo de resposta aceitável para acionamento de cargas resistivas que demandam muita potência da fonte  $V_{DD}$  (considerando que a frequência do sinal necessário na

# X Seminário de Extensão e Inovação XXV Seminário de Iniciação Científica e Tecnológica

#### 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

saída também seja baixa na ordem de dezenas de kHz). Este circuito (Figura 3) possui uma grande vantagem em relação ao inversor CMOS, neste caso, a amplitude do sinal de entrada não necessita ser o mesmo valor da tensão de alimentação do circuito. Com isso, torna-se possível o acionamento de cargas que demandam potência elevadas da fonte  $V_{DD}$  (até centenas de Watts), a partir de sinal de entrada próximo ao valor de 5 V, que é típico valor de tensão utilizado acionamento de dispositivos eletrônicos. Este fato não ocorre no inversor CMOS, visto que a amplitude do sinal utilizado em  $V_i$  deve ter o mesmo valor de  $V_{DD}$ .

#### **CONCLUSÕES**

Neste trabalho, comparou-se dois circuitos com atuações semelhantes: os inversores lógicos CMOS e nMOS, com o intuito de analisar as influências de frequência do sinal de entrada e de capacitância de carga na saída dos circuitos, nas características estáticas e dinâmicas dos inversores.

No inversor lógico CMOS, ao se utilizar um capacitor como carga, notou-se que este componente pode interferir no funcionamento do circuito devido a sua reatância capacitiva. Desse modo, o tempo de descarga do capacitor pode tornarse o limitador da frequência de trabalho, ao invés dos tempos de subida e de descida dos MOSFETs. Sendo assim, em aplicações de componentes miniaturizados, no qual os MOSFETs podem ser utilizados como resistores, sua capacitância de junção pode alterar o comportamento do circuito.

Para aplicações em baixas frequências (até algumas dezenas de kHz), o inversor nMOS obteve tempos de subida e de descida cerca de três ordens de grandeza maiores que o inversor CMOS. Esta característica pode não ser significativa em aplicações em eletrônica de potência, como em conversores estáticos CC-CA, pois como o circuito integrado do *driver* isola eletricamente o sinal de controle ao circuito principal em que a carga está conectada.

#### **AGRADECIMENTOS**

Os autores agradecem à Universidade Tecnológica Federal do Paraná, pela participação no Programa de Voluntariado em Iniciação Científica e Tecnológica e as empresas OrCAD Systems Corporation e a National Instruments pela disponibilização dos simuladores em versão do estudante, além da Originlab que disponibiliza de forma TRIAL o software Origin 2020b, que possibilitou a exposição dos dados obtidos computacionalmente.

#### **REFERÊNCIAS**

AHMED, A. **Eletrônica de potência**. 1. ed. São Paulo: Pearson, 2004. ISBN 9788587918031.

AKIYAMA, K. et al. First M87 event horizon telescope results. **The Astrophysical Journal Letters**, v. 875, n. 1, p. 1-17, 2019. DOI <u>10.3847/2041-8213/ab0ec7</u>. Acesso em 20 ago. 2020.

## X Seminário de Extensão e Inovação XXV Seminário de Iniciação Científica e Tecnológica

## 23 a 27 de Novembro | Toledo - PR

**CÂMPUS TOLEDO**

BOYLESTAD, R.L.; NASHELSKY, L. **Dispositivos eletrônicos e teoria de circuitos**. 11. ed. São Paulo: Pearson, 2013. ISBN 9788564574212.

INTERNATIONAL RECTIFIER. High and low side driver IR2110. *Datasheet...* [s.l.: s.n.], 23 mar. 2005. p. 1-24. Disponível em:

https://www.infineon.com/dgdl/Infineon-IR2110-DataSheet-v01\_00-EN.pdf?fileId=5546d462533600a4015355c80333167e&redirId=119801. Acesso em: 20 ago. 2020.

KOVAC, D; GLADYR, A. Half bridge driver for MOSFET and IGBT transistors. *In:* IEEE INTERNATIONAL CONFERENCE ON MODERN ELECTRICAL AND ENERGY SYSTEMS. **Anais...** Kremenchuk: IEEE, 2019. DOI <u>10.1109/MEES.2019.8896665</u>. Acesso em: 20 ago. 2020.

MARTINO, J.A.; PAVANELLO, M.A.; VERDONCK, P.B. Caracterização elétrica de tecnologia e dispositivos MOS. 1. ed. São Paulo: Thomson, 2003. ISBN 852210347X.

RAZAVI, B. **Fundamentos de microeletrônica**. 2. ed. São Paulo: LTC, 2017. ISBN 9788521633525.

SADIKU, M.N.; ALEXANDER, C.K. **Fundamentos de circuitos elétricos**. 5. ed. São Paulo: Bookman, 2013. ISBN 9788580551723.

SEDRA, A.S.; SMITH, K. C. **Microeletrônica**. 5. ed. São Paulo: Pearson, 2007. ISBN 9788576050223.

VISHAY SILICONIX. IRF 540. *Datasheet...* [*s.l.: s.n.*], 16 jun. 2008. p. 1-8. Disponível em: <a href="https://www.vishay.com/docs/91021/91021.pdf">https://www.vishay.com/docs/91021/91021.pdf</a>. Acesso em: 20 ago. 2020.

VISHAY SILICONIX. IRF 9540. *Datasheet...* [s.l.: s.n.], 20 jun. 2008. p. 1-8. Disponível em: https://www.vishay.com/docs/91078/91078.pdf. Acesso em: 20 ago. 2020.